1. Was ist HDI PCB?

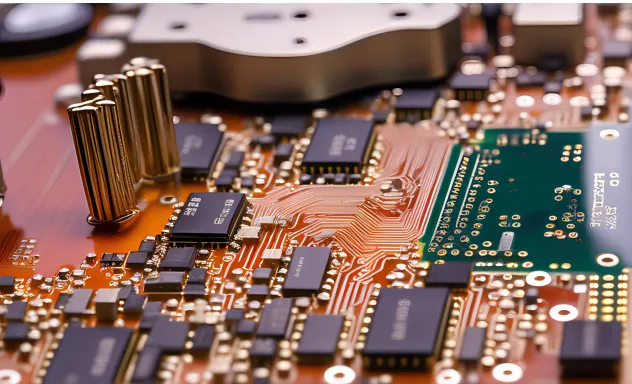

HDI-Leiterplatten (High-Density Interconnect) sind fortschrittliche Leiterplatten, die für die Unterbringung komplexer Elektronik auf kompaktem Raum ausgelegt sind. Im Gegensatz zu herkömmlichen Leiterplatten verwendet die HDI-TechnologieMikrovias(lasergebohrte Löcher <150μm),Fine-Pitch-Leiterbahnen(Strichstärke/-abstand ≤75μm) undsequentielle LaminierungUm Verdrahtungsdichten von mehr als 20.000 Verbindungen pro Quadratzoll zu erreichen.

Wichtige strukturelle Merkmale:

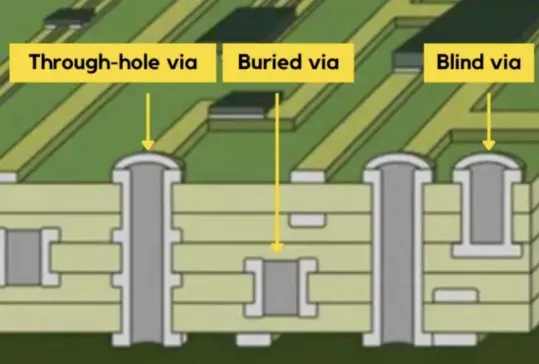

- Blinde/vergrabene Durchkontaktierungen: Reduzieren Sie Lagenübergänge, indem Sie benachbarte Schichten verbinden, ohne die gesamte Platine zu durchdringen.

- Dünne Dielektrika: Materialien wie Megtron 6 oder Isola 370HR mit Dk ≤3,5 für Signalintegrität.

- Via-in-Pad: Platziert Durchkontaktierungen direkt unter den Komponentenpads, um Platz zu sparen.

Anträge:

- Smartphones (z. B. der 10-Layer-HDI-Stackup des iPhone 15).

- Medizinische Implantate (Herzschrittmacher mit Komponenten im Rastermaß 0,4 mm).

- ADAS-Systeme für die Automobilindustrie (Teslas Autopilot-Module).

2. Was sind gestapelte, versetzte und übersprungene Durchkontaktierungen in HDI PCB?

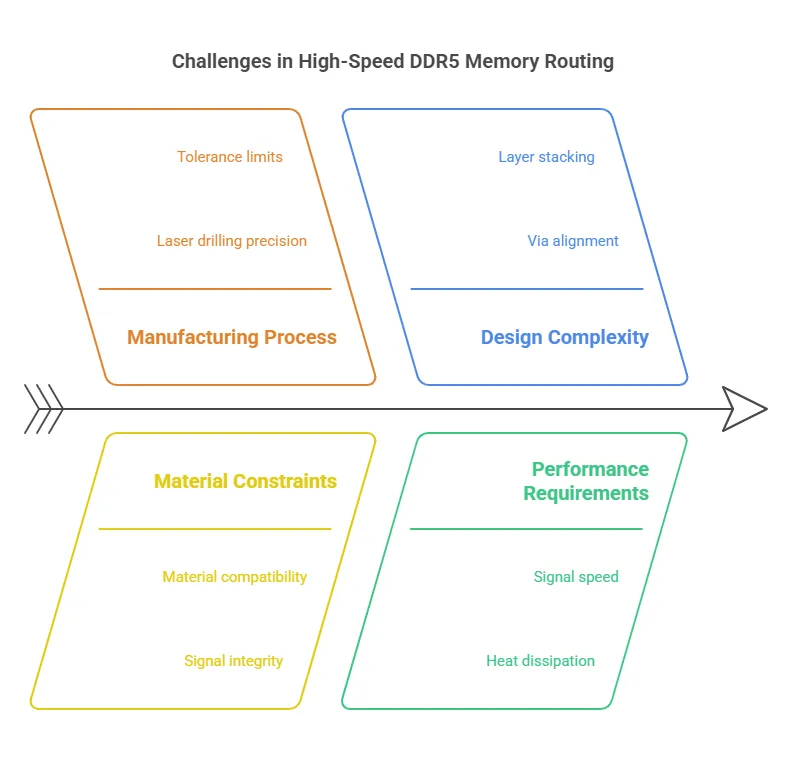

Gestapelte Durchkontaktierungen:

Vertikale Ausrichtung von Microvias über mehrere Schichten.

- Anwendungsfall: Hochgeschwindigkeits-DDR5-Speicher-Routing.

- Einschränkung: Erfordert präzises Laserbohren (±25μm Toleranz).

Gestaffelte Durchkontaktierungen:

Versetzen Sie Microvias zwischen den Schichten, um die Spannungskonzentration zu reduzieren.

- Vorteil: Verbessert die thermische Zuverlässigkeit um 30 % (IPC-6012E).

- Design-Regel: Mindestens 150 μm Abstand zwischen benachbarten Durchkontaktierungen.

Durchkontaktierungen überspringen:

Microvias, die Zwischenschichten "überspringen", um nicht benachbarte Schichten zu verbinden.

- Anwendung: HF-Frontend-Module in 5G-Basisstationen.

- Risiko: Erhöhte Kapazität bei einem Anti-Pad-Abstand <100 μm.

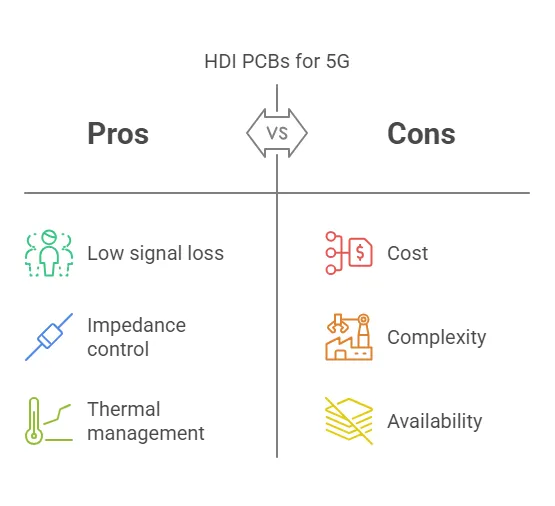

3. Warum HDI-Leiterplatten für 5G-Kommunikationsgeräte unerlässlich sind

Anforderungen an 5G-mmWave-Frequenzen (24–40 GHz):

- Geringer Signalverlust: Die extrem geringe Rauheit von Kupfer (≤0,5 μm Ra) von HDI minimiert die Verluste bei Skin-Effekten.

- Impedanzkontrolle: Enge Toleranz von ±5 % unter Verwendung von Hybrid-Rogers/FR-4-Materialien.

- Thermisches Management: 2W/m·K wärmeleitende Substrate (z.B. Arlon 85N) für Leistungsverstärker.

Auswirkungen auf die reale Welt:

- Die 5G-mMIMO-Funkgeräte von Ericsson verwenden 14-Layer-HDI-Leiterplatten, um 64T64R-Antennenarrays zu erreichen.

- Die Nichteinführung von HDI führt zu 15 bis 20 % langsameren Datenraten (Qualcomm 2023 Whitepaper).

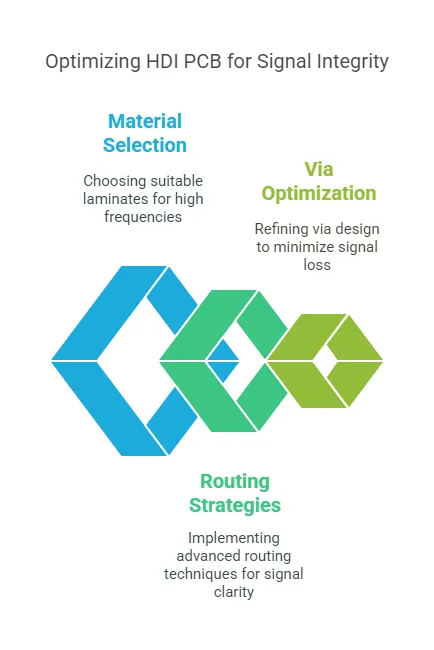

4. Wie HDI PCB die Signalintegrität in Hochfrequenzanwendungen verbessert

Schritt-für-Schritt-Optimierung:

-

Materialauswahl:

- Wählen Sie Laminate mit Df ≤0,002 bei 10 GHz (z. B. Panasonic Megtron 7).

- Vermeiden Sie FR-4 für Frequenzen >5 GHz.

-

Routing-Strategien:

- WerkzeugDifferentielle Paaremit einer Längenanpassung von ≤50μm.

- Gebrauchengeschirmte Leiterbahnenfür 28GHz+ Signale.

-

Über Optimierung:

- Backdrillen Sie ungenutzte Through-Stubs >85 % zurück (kritisch für PCIe 6.0).

- Anwendenüber Zeltenmit Lötstopplack zur Kapazitätsreduzierung.

Messbare Ergebnisse:

- 40 % geringeres Übersprechen in 25-Gbit/s-SerDes-Verbindungen.

- 0,5 dB Reduzierung der Einfügedämpfung bei 28 GHz.

5. Was ist AOI (Automated Optical Inspection) bei der Herstellung von HDI-Leiterplatten?

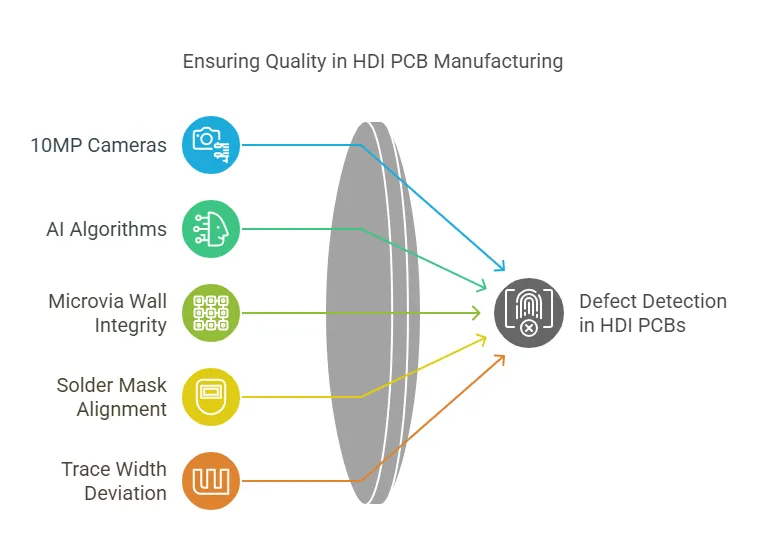

AOI-Systeme verwenden 10-MP-Kameras und KI-Algorithmen, um Defekte in HDI-Platinen zu erkennen:

Kritische Prüfpunkte:

- Microvia Wandintegrität: Risse >10μm gekennzeichnet (gemäß IPC-A-600).

- Ausrichtung der Lötstoppmaske: Toleranz ±35μm.

- Abweichung der Leiterbahnbreite: >±15 % ab abgelehntem Design.

AOI-Arbeitsablauf:

- Scan vor der Laminierung: Überprüft die Registrierung der inneren Schicht.

- Scan nach dem Ätzen: Überprüft die Leiterbahngenauigkeit von 75 μm.

- Endkontrolle: 3D-Höhenmapping für BGA-Koplanarität.

Branchendaten:

- AOI reduziert die HDI-Ausschussraten von 8 % auf 1,2 % < (Bericht Shennan Circuits 2024).

- Die Falschanrufrate <0,3 % mit Deep-Learning-Modellen.